رجیسترها

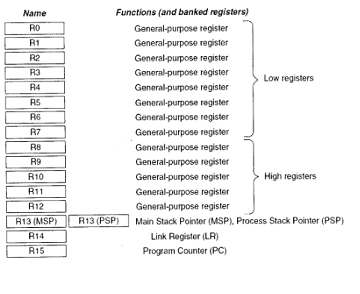

پردازنده Cortex-M3 دارای رجیسترهای R0 تا R15 می باشد . R13 اشاره گر پشته است و در یک زمان تنها یک کپی از آن قابل رویت است.

1-1-2 R0 تا R12 رجیسترهای عمومی :

R0 تا R12 رجیسترهای عمومی 32 بیتی برای عملیات های داده هستند . دستورالعمل Thumb 16 بیتی تنها می تواند به یک زیر مجموعه از این رجیسترها دست پیدا کند.

2-1-2 R13 اشاره گر پشته :

Cortex-M3 دارای دو اشاره گر پشته است .در یک زمان تنها یک اشاره گر قابل رویت می باشد.

اشاره گر پشته اصلی : این اشاره گر ،اشاره گر پشته پیش فرض است که توسط هسته اصلی سیستم عامل و اداره کننده استثناء مورد استفاده قرار می گیرد.

اشاره گر پشته فرآیند : این اشاره گر توسط کد برنامه کاربردی کاربر مورد استفاده قرار می گیرد.

دو بایت پایینی در اشاره گر پشته همواره صفر است . به این معنا که آنها همواره به صورت کلمه همتراز شده اند.

3-1-2 R13 رجیستر پیوند :

زمانی یک زیر روال فراخوانی می شود آدرس برگشتی در رجیستر پیوند ذخیره می شود.

4-1-2 R15 شمارنده برنامه :

شماره برنامه ،آدرس برنامه جاری می باشد .از این رجیستر می توان برای کنترل روند برنامه استفاده نمود.

شکل 1-2 رجیسترها در Cortex-M3

2-2 رجیستر های خاص :

پردازنده Cortex-M3 همچنین دارای تعدادی رجیستر خاص می باشد (طبق شکل زیر) :

رجیستر های وضعیت برنامه .

رجیسترهای پوشش وقفه .

رجیستر کنترل .

این رجیسترها دارای توابع خاصی هستند که تنها از طریق دستورالعمل خواص می توان به آنها دسترسی پیدا کرد. رجیسترهای خواص را نمی توان برای عملیات های معمولی داده ها به کار برد (جدول 1-2 را ببینید ).

شکل 2-2 رجیستر های خاص در Cortex-M3

جدول 1-2 رجیسترهای خواص و عملکرد آنها

رجیستر عملکرد

xPSR پرچم های پردازش حسابی و منطقی (پرچم صفر و پرچم نقلی) ، وضعیت های اجرا و شماره وقفه در حال اجرای جاره را ارایه می کند.

PRIMASK تمام وقفه های به جزء وقفه غیر قابل پوشش و hard fault را غیر فعال می کند.

FAULTMASK تمام وقفه ها به جزء NMI را غیر فعال می کند.

BASEPRI تمام وقفه ها با سطح الویت خاص یا سطح الویت پایین تر را غیر فعال می کند.

CONTROL وضعیت ممتاز و انتخاب اشاره گر پشته را تعریف می کند.

1-2-2 رجیسترهای عمومی R0 تا R7 :

رجیسترهای عمومی R0 تا R7 رجیسترهای پایین نیز نامیده می شوند. این رجیسترها از طریق دستور Thumb 16 بیتی و تمام دستورالعمل های Thumb-2 32 بیتی قابل دسترسی می باشند. تمام این رجیسترها 32 بیتی هستند و مقدار Reset غیر قابل پیش بینی است .

2-2-2 رجیسترهای عمومی R8 تا R12 :

رجیسترهای عمومی R8 تا R12 رجیسترهای بالا نیز نامیده می شوند . این رجیسترها از طریق تمام دستورالعمل های Thumb2 قابل دسترس می باشند ، اما از طریق دستورالعمل های Thumb 16 بیتی قابل دسترسی نمی باشند . تمام این رجیسترها 32 بیتی می باشند. مقدار Reset غیر قابل پیش بینی است

R13 یک اشاره گر پشته است . پردازنده Cortex-M3 دارای دو اشاره گر پشته است . این دو امکان بر پایه دو حافظه پشته جداگانه فراهم کنند. زمانیکه رجیستر R13 استفاده می شود شما تنها می توانید به اشاره گر پشته پشته جاری دسترسی داشته باشید ، اشاره گر پشته دیگر قابل دسترسی نمی باشد مگر اینکه از دستورالعمل های خاص برای انتقال ار رجیستر عمومی به رجیستر خاص یا انتقال از رجیستر خاص به رجیستر عمومی استفاده نماید .

دو اشاره گر پشته عبارتند از :

اشاره گر پشته اصلی یا SP_MAIN در مستندات ARM : این اشاره گر پشته ، اشاره گر پشته پیش فرض است که توسط هسته سیستم عامل اداره کننده استثنا و تمام کدهای برنامه کاربردی که به دسترسی ممتاز نیاز دارند مورد استفاده قرار می گیرد.

اشاره گر پشته فرآیند یا SP_ProCess در مستندات ARM : این اشاره گر توسط کد برنامه کاربردی سطح پایین مورد استفاده قرار می گیرد ( زمانیکه اداره کننده استثنا در حال اجرا نیست )

استفاده از هر دو اشاره پشته ضروری نمی باشد . یک برنامه کاربردی ساده می توانند به طور کامل به MSP تکیه کرده و از آن استفاده کنند ، اشاره گر های پشته برای دسترسی به پروسه های حافظه مانند PUSH و POP به کار می روند.

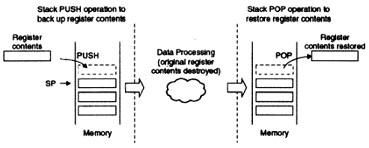

3-2 PUSH و POP پشته :

پشته یک مدل از کاربرد حافظه است . در حقیقت ، پشته یک بخش ساده از حافظه سیستم است و از یک رجیستر اشاره گر (درون پردازنده ) استفاده می کند تا پشته به عنوان یک بافر اولین ورودی – آخرین خروجی عمل کند . کاربرد معمول پشته ، ذخیره کردن محتوای رجیستر قبل از پردازش داده ها می باشد و بعد از این که عمل پرداز انجام شد این محتوات را از پشته بر می گرداند .

مفهوم کلی حافظه پشته

زمانیکه عملیات های PUSH و POP در حال انجام است ، رجیستر اشاره گر پشته نامیده می شود به طور خودکار تنظیم می شود تا از خراب شدن یا از بین رفتن داده های قبلی انباشته شده در پشته بواسطه عملیات های پشته بعدب جلوگیری کند .

در Cortex-M3 ، دستورالعمل های دسترسی به حافظه پشته PUSH و POP هستند . قواعد دستوری زبان اسمبلی به صورت زیر است :

PUSH {R0} ; R13 = R13 – 4 , then memory [R13] = R0

POP {R0} ; R0 = memory [R13] , then R13 = R13 +4

Cortex-M3 از یک آرگومان پشته کامل نزولی استفاده می کند ، بنابراین تا زمانیکه داده جدید در پشته ذخیره می شود اشاره گر پشته کاهش می یابد . PUSH و POP معمولاٌ برای ذخیره کردن محتوای رجیستر در حافظه پشته در ایتدای زیر روال و سپس باز گرداندن رجیسترها از پشته در انتهای زیر روال بکار می روند. شما می توانید چندین رجیستر را در یک دستوراعمل ، PUSH یا POP کنید .

Sub Routine_1

PUSH {R0-R7,R12,R14} ; save registers

… ; Do you Processing

POP {R0-R7,R12,R14} ; Restore Register

BX R14 ; Return to calling function

به جای استفاده از R13 ، شما می توانید از SP در کد برنامه خود استفاده کنید . در کد برنامه ، MSP و PSP هر دو می توانند R13/SP را فراخوانی کنند . هر چند شما می توانید به یک چیز خاص به کمک دستور العمل های دستوری رجیستر دسترسی پیدا کنید .

در مسندات ARM ، MSP ، SP_Main نیز نامیده می شود . پس از روشن شدن سیستم ، MSP اشاره گر پشته پیش فرض است که توسط کد هسته و اداره کننده استثناء مورد استفاده قرار می گیرد . PSP یا SP_Process در مستندات ARM ، معمولا توسط پردازش های Thread در یک سیستم دارای سیستم عامل استفاده می شود.

از آنجا که عملیات های PUSH و POP همواره به صورت کلمه همتراز شده هستند (آدرس های آنها باید 0x0 باشد) بیت صفر و یک در SP\R13 به صورت سخت افزاری با صفر تنظیم شده است و همواره به عنوان صفر خوانده می شود .

4-2 R14 رجیستر پیوند :

R14 یک رجیستر پیوند است . در برنامه اسمبلی ، شما می توانید این رجیستر را به صورت R14 یا LR بنویسید . زمانیکه یک زیر روال یا تابع فراخوانی شده ، LR برای ذخیره کردن شمارنده برنامه بازگشتی مورد استفاده قرار می گیرد . به عنوان مثال ، زمانیکه از دستورالعمل انشعاب و پیوند استفاده می کنید.

Main ; Main program

…

BL Function 1 ; Call Function using branch with link instruction

;PC=Function 1 and

;LR = the next instruction in main

…

Function 1

… ; program code for function 1

BX LR ; Return

علی رغم اینکه بیت صفر شمارنده همواره صفر است ( زیرا دستورالعمل های word Aligned یا half word aligned هستند ) ، بیت صفر در LR همواره قابل خواندن و نوشتن است . علت این موضوع در مجموعه دستور العمل های Thumb می باشد . بیت صفر اغلب برای نماشی وضعیت ARM/Thumb استفاده می شود . برای اینکه Thumb-2 در Cortex-M3 یا سایر پردازنده ARM که از تکنولوژی Thumb-2 پشتیبانی می کنند کار کند ، LSB ( کم ارزشترین بیت ) قابل خواندن و نوشتن است .

5-2 R15 شمارنده برنامه :

R15 یک شمارنده برنامه است . در کد اسمبلی شما می توانید از طریق R15 یا PC به آن دسترسی داشته باشید . به این دلیل طبیعت لوله کشی شده پردازنده Cortex-M3 ، زمانیکه شما این رجیستر را می خوانید ، خواهید دید که معمولاٌ اختلاف مقدار با محل دستورالعمل های اجرایی چهار می باشد .

به عنوان مثال :

0x1000 : mov R0,PC ; R0 = 0x1004

مشخصات

- تولید و فروش گچ پلیمری

- webdes

- داروخانه پلاس | داروخانه آنلاین شبانه روزی

- ترشیز وب

- بانک اطلاعات مشاغل

- لباس زیر شیردهی نخی یقه دار زنانه خالدار

- تیم والیبال کاراسونو

- تک تاک

- شرکت کالای صنعت نفت

- محصولات کیهان

- delsatecco.rozblog.com

- قفل دیجیتال

- فارسروید

- beroozha

- Rank2Game

- پویان اسکنر

- lilini

- تعمیر و فروش

- kiamehr85

- دانلود رایگان کتاب

- ویلم

- پچ لیگ برتر ایران

- تفریحی و دانلود

- کنترلی کردن درب آپارتمان

- فن کویل